Latches and Flip-Flops(锁存器和D触发器)

(资料图片仅供参考)

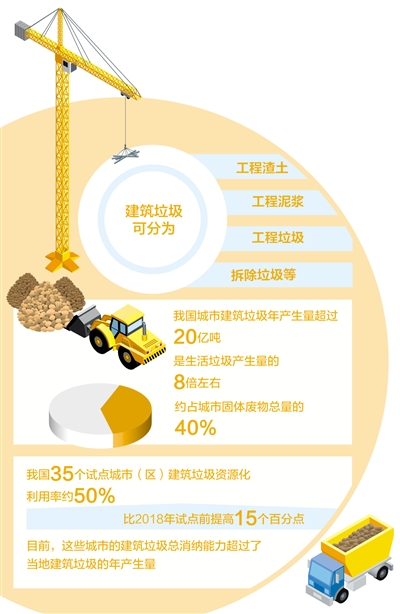

(资料图片仅供参考)

D触发器

Dff

Dff8(8位输入输出的d触发器)

Dff8r(高电平同步复位功能的8位D触发器)

Dff8p(同步 下降沿 重置为0x34)

Dff8ar

(高电平异步复位功能的8位D触发器)

Dff16e

Exams/m2014 q4a

锁存器

DFF (Exams/m2014 q4b)

AR 代表 asynchronous reset,所以这是一个带有异步复位的 D 触发器,我们在先前的题目中讨论过异步复位的问题。

异步复位的 D 触发器

DFF (Exams/m2014 q4c)

R 代表 synchronous reset,(就不用 SR 或者 SSR 表示了)所以这是一个带有同步复位的 D 触发器,我们在先前的题目中讨论过同步复位的问题。

Exams/m2014 q4d

Mux and DFF位移寄存器

Mux and DFF

考虑一个 n-bit 移位寄存器。

DFFS and gates

如下图所示的状态机,假设D触发器在状态机启动之前初始化为0,实现该电路:

Create circuit from truth table

JK触发器具有置0、置1、保持和翻转功能

Detect an Edge//

上升沿的检测方法

Detect both edges

Edge capture register

Dual-edge triggered flip-flop

双边沿检测:一种是用MUX,一种是用XOR

关键词: